A Comprehensive Analysis of Current Spikes in a Split-Phase Inverter

Abdul Basit Mirza, Asif Imran Emon, Sama Salehi Vala and Fang Luo

2022 IEEE Applied Power Electronics Conference and Exposition (APEC), 2022

Read Here

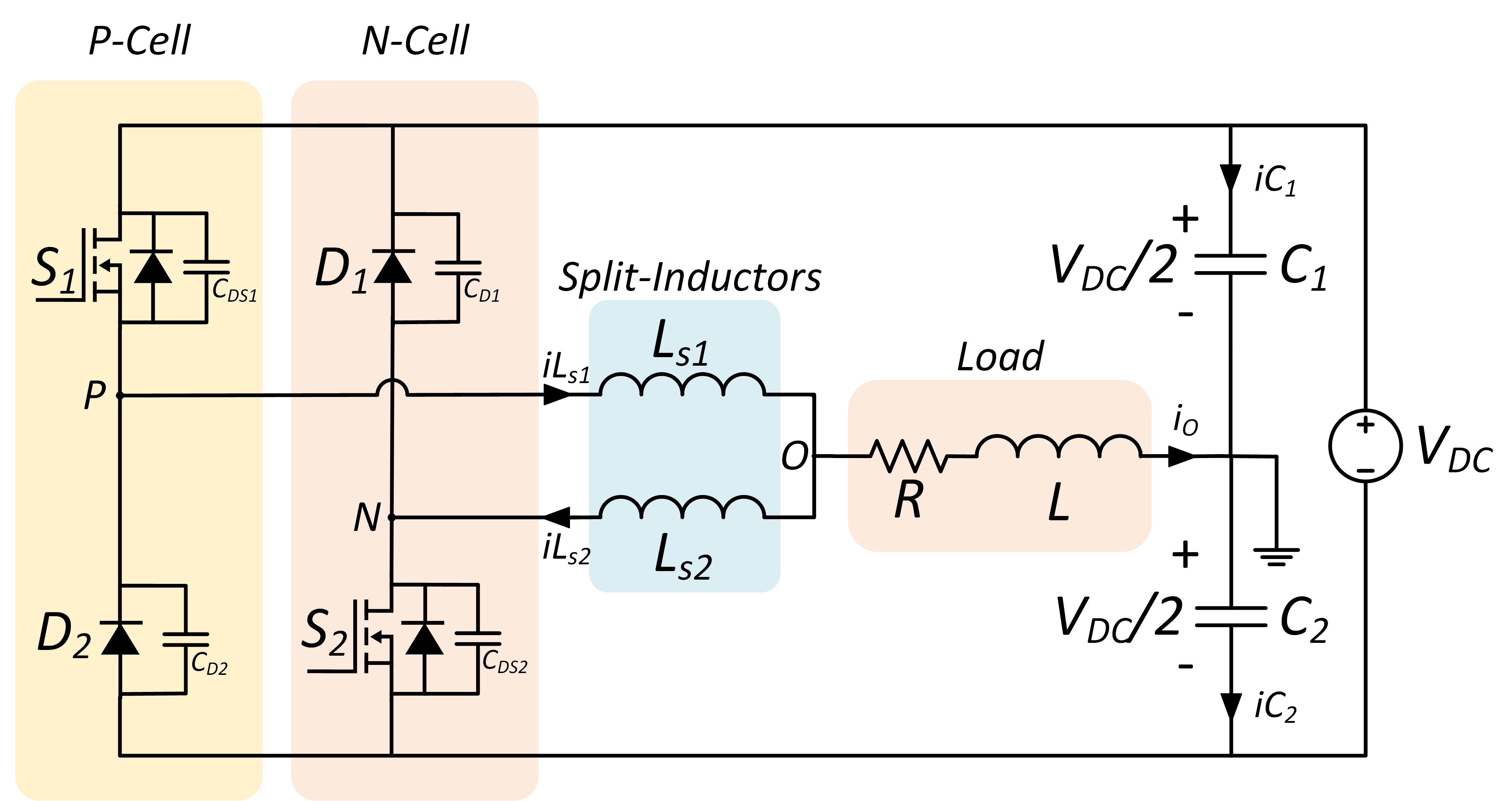

Abstract: Compared with a conventional two-level inverter, split-phase inverter decouples the top and bottom switches and antiparallel diodes in a phase leg through addition of split inductors. These split inductors prevent current shoot-through with zero deadtime operation, which lowers the distortion in the output waveforms and makes this topology ideal for fast-switching devices such as SiC or GaN. Further, decoupling between top and bottom device's output capacitance also results in lower overall switching loss and improves Electromagnetic Interference (EMI) performance. However, the split inductors experience current spikes during switching transition, which can lead to significant core loss. This paper presents a comprehensive analysis of current spikes in a split phase inverter with SPWM, characterized by the load power factor (PF). The proposed model can be used to optimize the size of split inductor. At first, the circuit of a single phase-leg with split inductors, is analyzed and a mathematical model for spike current estimation is proposed. The proposed model is verified on a SiC-based hardware prototype switching at 72 kHz. It is shown that the spike amplitude depends on the load PF as well as on the values of the split inductors and parasitic capacitances of the power semiconductors. Lastly, the proposed model is extended to the three-phase configuration.

Recommended citation (BibTex):

@INPROCEEDINGS{MirzaAPEC2022,

author={Mirza, Abdul Basit and Emon, Asif Imran and Vala, Sama Salehi and Luo, Fang},

booktitle={2022 IEEE Applied Power Electronics Conference and Exposition (APEC)},

title={A Comprehensive Analysis of Current Spikes in a Split-Phase Inverter},

year={2022},

volume={},

number={},

pages={1580-1585},

doi={10.1109/APEC43599.2022.9773407}

}